Awesome

hdlConvertor

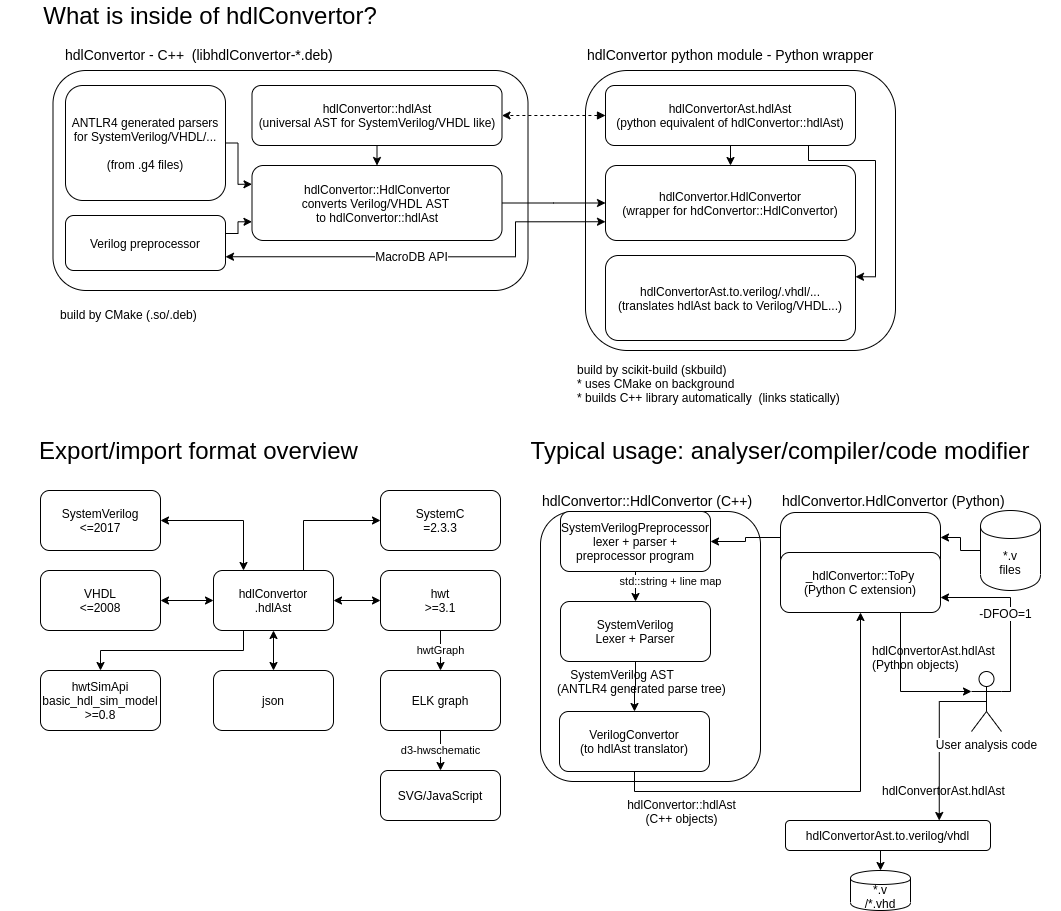

This library is a System Verilog and VHDL parser, preprocessor and code generator for Python/C++. It contains:

- ANTLR4 generated VHDL/(System) Verilog parser with full language support.

- Convertors from raw VHDL/SV AST to universal HDL AST (hdlConvertor::hdlAst and it's python equivalent.).

- Convertors from this HDL AST to SV/VHDL/JSON and other formats.

- Compiler focused utils for manipulation with HDL AST.

- HdlAstVisitor, id resolution, sensitivity detection, vhdl <-> verilog type conversion, ...

Supported languages:

- IEEE 1076-2008 (VHDL 2008) and all previous standard, (currently without

tool_directiveandPSL) - [IEEE 1076-2019] WIP

- IEEE 1800-2017 (SystemVerilog 2017) and all previous standards.

Installation

Linux: Installing dependencies (Ubuntu 20.10)

# we recommend to use gcc>=9, Visual Studio 2017 or equivalent

sudo apt install build-essential uuid-dev cmake default-jre python3 python3-dev python3-pip libantlr4-runtime-dev antlr4 ninja-build

Installing this library

# note this may be older version than you see in repo

sudo pip3 install hdlConvertor

# or download repository and run

sudo pip3 install --upgrade --force-reinstall --no-cache-dir git+https://github.com/Nic30/hdlConvertorAst.git

sudo pip3 install -r requirements.txt

sudo python3 setup.py install

# if you are using version from git rather uninstall

# old library first if required

# sudo pip3 uninstall hdlConvertor

Installer also supports other options which may be usefull

python setup.py install --prefix /tmp/python_install/ --build-type Debug -- -DANTLR_JAR_LOCATION=/antlr-4.7.1-complete.jar -- VERBOSE=1

You can also install only C++ library/generate .deb package (nothing specific, just normal cmake-based library)

mkdir build && cd build

cmake .. && cmake . --build

cpack # to generate .deb package

Windows:

Take a look at appveyor.yml and doc/windows_installation_and_build.rst. It is required to download antlr4 first and have visual studio or other c++ compiler installed.

Usage

The HDL AST (the parsed code) is represented by objects from hdlConvertor.hdlAst. Parsing and code modification is straightforward, as you can see in following example

Similar projects:

(Tell us If you know about some other project!)

- circt - C++, LLVM based infrastructutre for SV/VHDL/FIRRTL compilation and simulation

- cl-vhdl - lisp, Parser of VHDL into lisp-expressions

- HDL_ANTLR4 - C# projects that use ANTLR4 library to analyse VHDL and Verilog code

- hdlparse - vhdl/verilog parser in python

- ieee1800_2017 - Java, SystemVerilog preprocessor

- istyle-verilog-formatter - c++, Verilog formatter

- Pyverilog - python verilog toolkit

- pyvsc - C++, library for Verification Stimulus and Coverage description

- pyVHDLParser - python vhdl parser with 2008 support

- RgGen - CSR (Configuration and Status Registers) generator

- rust_hdl - rust vhdl 2008 parser

- slang - Parser and compiler library for SystemVerilog.

- sv-parser - Rust, SystemVerilog parser library fully complient with IEEE 1800-2017

- sv2chisel - Scala, SystemVerilog to Chisel translator

- systemc-clang - SystemC Parser using the Clang Front-end

- v2sc - vhdl to systemc

- veelox - Java+ANTLR, An experiment in SystemVerilog Preprocessing

- verible -C++, SystemVerilog parser, style-linter, and formatter

- verilog-parser - A Flex/Bison Parser for the IEEE 1364-2001 Verilog Standard.

- vbpp - C, Verilog PreProcessor

- tree-sitter-verilog - JS, Verilog grammar for tree-sitter

- Verilog-Perl

- vpp.pl - verilog preprocessor with integrated Perl

- sv2v- Haskell, SystemVerilog to Verilog

- Surelog - C++, System Verilog 2017 Pre-processor and parser

- UHDM - rust, universal hardware data model

- HDLParserSharp - C#, VHDL/SV -> universal AST